|

The

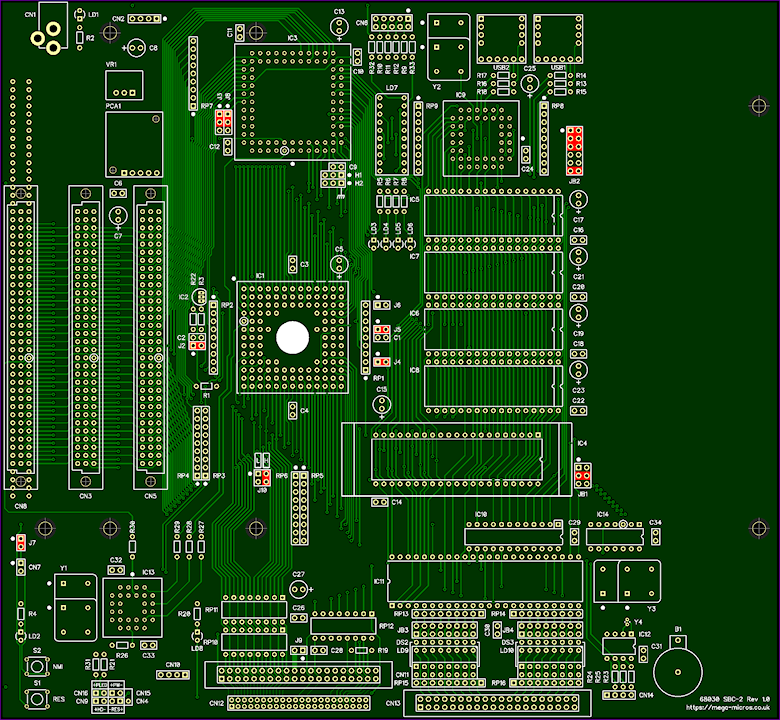

68030 SBC-2 |

| Jumpers |

| |

|

Default settings: |

place Jumpers as

shown in RED below |

|

|

|

|

|

J2 BE - Bus

Error |

| |

|

This Jumper

enables/disables the bus error logic. |

| |

|

J2 open - disabled |

|

J2 short - enabled |

| |

|

J3 DS1 - DSACK1 |

| |

|

This Jumper allows

DSACK1 to be grounded for test purposes. |

| |

|

J3 pins 1-2 short

- normal operation |

|

J3 pins 2-3 short

- DSACK1 grounded |

| |

|

J4 CACHE |

| |

|

This Jumper

enables/disables the 68030 instruction and data caches. |

| |

|

J4 open - enabled |

|

J4 short - disabled |

| |

|

J5 MMU - Memory

Management Unit |

| |

|

This Jumper

enables/disables the 68030 memory management unit. |

| |

|

J5 open - enabled |

|

J5 short - disabled |

| |

|

J6 BVD - Boot

Vector Disable |

| |

|

This Jumper

enables/disables the BV (Boot Vector) mode. |

| |

|

J6 open - normal

operation |

|

J6 short - RAM

disabled + ROM fixed at 0x000000 |

| |

|

J7 NMI - Non

Maskable Interrupt |

| |

|

This Jumper

enables/disables interrupts from the NMI pushbutton and NMI header. |

| |

|

J7 open - disabled |

|

J7 short - enabled |

| |

|

J8 DS0 - DSACK0 |

| |

|

This Jumper allows

DSACK0 to be grounded for test purposes. |

| |

|

J8 pins 1-2 short

- normal operation |

|

J8 pins 2-3 short

- DSACK0 grounded |

| |

|

J9 PWR - IDE

Power |

| |

|

Power (5V DC) is

routed to CN11 (IDE-40W) pin 20 when this Jumper is

shorted. |

| |

|

J10 TERM - Data Bus

Bias |

| |

|

This Jumper

controls the bias applied to the 68030 data bus. |

| |

|

J10 pins 1-3 short

- 68030 data bus biased low |

|

J10 pins 2-4 short

- 68030 data bus biased high |

| |

| JB1 RCFG -

ROM Configuration |

| |

|

This Jumper Block allows

the installed ROM to be configured as one large ROM or two smaller

Jumper selectable ROM's. |

| |

|

3-4 short |

4MB ROM |

This is

the default

setting for all standard Mega-680x0 System ROM's |

|

1-2 short |

2MB ROM_A * |

|

Upper |

2MB of

4MB ROM mapped to address space |

|

|

5-6 short |

2MB ROM_B * |

|

Lower |

2MB of

4MB ROM mapped to address space |

|

|

| |

|

* The ROM repeats

twice within the 4MB address space |

| |

| JB2 STXSF -

Serial TX & Software Features |

| |

|

The following JB2

links control serial data transmission from the board: |

| |

|

1-2 short |

USB1

(CON) TX enabled |

|

3-4 short |

USB2

(AUX) TX enabled |

|

| |

|

The remaining JB2

links control software features within System ROM V2.0x

as follows: |

| |

|

5-6 short |

115K baud DUART (XR68C681) support enabled |

|

7-8 short |

N/A |

|

9-10 short |

ROM diagnostics

(Slow Boot)

enabled |

|

11-12

short |

ACRTC

graphics test

enabled |

|

|

| |

| |